【会员风采】韬略科技 | RE时钟高次谐波解决方案(韬这个字怎么读?)

(来源:深圳市汽车电子行业协会)

一

前言

时钟信号是时序逻辑的基础,它作为数字电路系统的心脏,在数字电路中具有重要意义。时钟信号在数字系统中并非完美的方波,其快速边沿(上升/下降时间)包含了极其丰富的高次谐波成分。这些高次谐波虽然对数字电路的逻辑功能没有直接影响,但在电磁兼容(EMC)和信号完整性(SI)中带来了显著的危害与痛点。

图1 时钟

二

时钟高次谐波解决方案

针对这种高次谐波的时钟最有效的手段就是展频技术(SSC)。

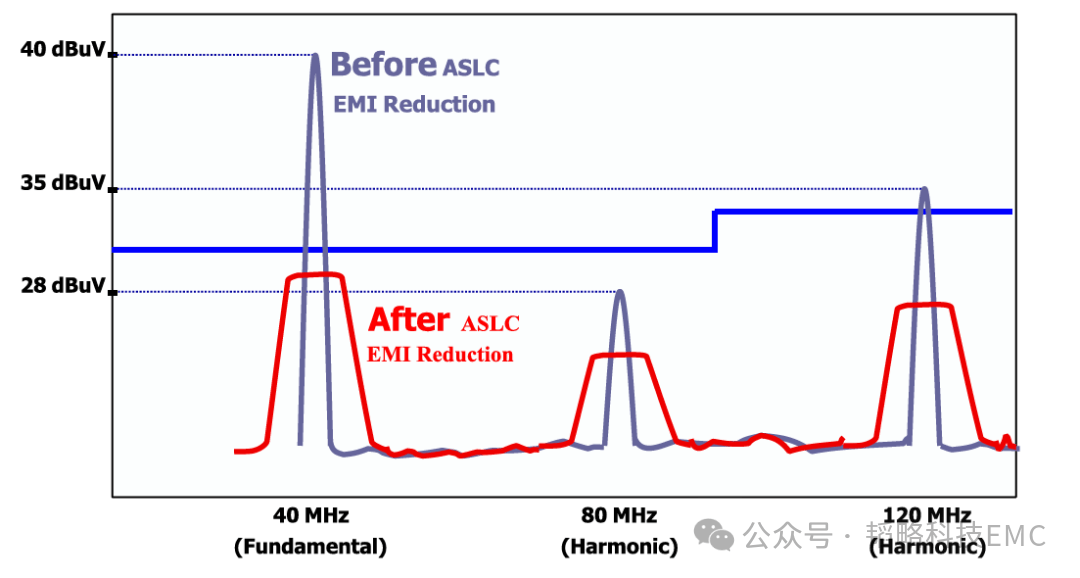

展频技术是让时钟频率在极小的范围内周期性调制,将能量分散到更宽频带,从而达到降低尖峰能量。展频技术可以让我们从源头去解决时钟噪声问题,针对时钟的高次谐波效果更好,每次谐波展频抑制效果都会得到加强。

图2 展频效果

现在很多SOC芯片方案都能支持软件展频,通过软件设置对时钟信号进行调制,从而达到展频效果。但从很多客户反馈来看,软件展频的效果都不尽人意,从而导致很多工程师对展频技术失去了信心。

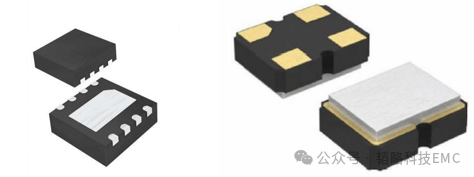

目前比较主流的还是使用硬件展频去针对时钟,而硬件展频一种是展频IC针对主时钟(晶振信号)进行展频后提供给主控;另一种就是展频晶振,它会带展频效果的有源晶振,可以直接输出带展频效果的时钟信号给主控。

图3 展频IC与展频晶振

三

案例分享

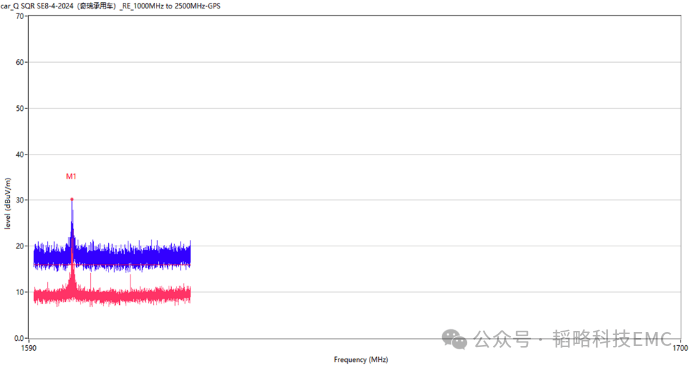

这次分享的是一个车机与中控屏一套的产品,下图是摸底数据:

图4 摸底数据

产品测试问题点在1G以上的频段,频点为1597M。通过排查我们发现只要插了视频线就会存在这个频点,然后近场频谱测试把问题锁定在SOC输出的视频信号到串行器 (SERializer)这一部分存在对应频点。

图5 简单图示

针对这里的视频走线信号进行了RC滤波、屏蔽等措施都没有效果,发现就算在这一段滤波抑制下来的能量会被串行器 (SERializer)进行增强后串行传输出去,导致滤波等措施没有效果。

图6 展频晶振措施

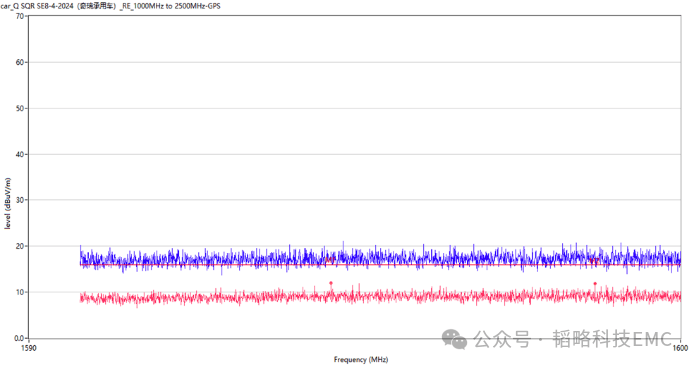

既然从数据传输路径去抑制没有效果,那就只能从时钟源头去抑制,就用上我们的展频晶振产品demo对SOC的参考时钟27M无源晶振进行替换验证。

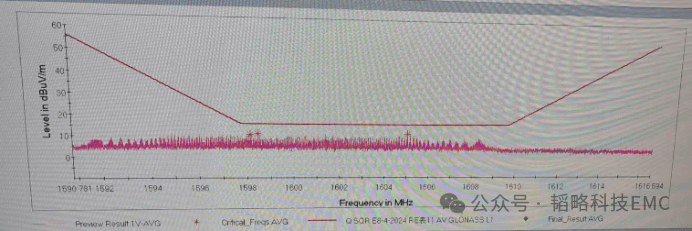

图7 整改数据

图8 客户第三方验证数据

【分析】:

从源头时钟进行展频,所有参考此时钟的时钟信号都会有展频效果,其高次谐波的时钟信号展频效果更优,能量强度抑制更好。串行器 (SERializer)接收到的也是展频过后的时钟信号,同时因为它接收到的时钟信号高次谐波的能量强度更低,就算经过串行器增益过后的能量强度也不会太高。

四

总结

时钟信号的高次谐波是数字系统电磁兼容性设计中的”隐形杀手”。其危害主要在于逐渐严格要求的电磁辐射和传导干扰测试标准中导致产品认证失败、系统性能下降甚至功能失效。在高速信号时代,时钟设计、电路选择、PCB布局布线、电源设计、屏蔽滤波等多个环节采取综合措施,并在性能和EMC之间找到最佳平衡点,这是一个持续性的挑战。

关于韬略

致力于提供一站式EMC解决方案

●技术服务 ●实验检测

●企业培训 ●器件销售

运用新型产品 走在时代前沿!

欢迎咨询!

Tel:0755-82908734

Moblie:13417580974